液压万能试验机

本申请实施例涉及半导体技术领域,具体涉及一种理想二极管电路,该理想二极管电路包括:相互电连接的电容单元与晶体管单元;电压变换单元分别与电容单元与晶体管单元电连接,电压变换单元用于通过晶体管单元中的寄生二极管对电容单元充电;控制单元的输入端与电容单元电连接,控制单元的输出端与晶体管单元的控制端电连接,控制单元用于基于电容单元的电压信号输出第一驱动信号或第二驱动信号,并在第一驱动信号的作用下驱动晶体管单元关闭,在第二驱动信号的作用下驱动晶体管导通,反偏截止驱动单元在晶体管单元两端的电压反向时驱动晶体

电压变换单元,所述电压变换单元分别与所述电容单元与所述晶体管单元电连接,所

控制单元,所述控制单元的输入端与所述电容单元电连接,所述控制单元的输出端与

所述晶体管单元的控制端电连接,所述控制单元用于基于所述电容单元的电压信号输出第

一驱动信号或第二驱动信号,并在所述第一驱动信号的作用下驱动所述晶体管单元关闭,

反偏截止驱动单元,所述反偏截止驱动单元的输入端与所述电容单元的第一端电连

接,所述反偏截止驱动单元的输出端与所述晶体管单元的控制端电连接,所述反偏截止驱

2.根据权利要求1所述的理想二极管电路,其特征是,所述反偏截止驱动单元包括:

反偏检测电路,所述反偏检测电路的第一输入端与所述晶体管单元的控制端电连接,

所述反偏检测电路的第二输入端与所述晶体管单元的电压量测端电连接,所述反偏检测电

第一关断器件,所述第一关断器件的输入端与所述反偏检测电路的输出端电连接,所

述反偏检测电路的输出端与所述晶体管单元的控制端电连接,所述第一关断器件用于在所

触发电路,所述触发电路的控制端与所述电容单元的第一端电连接,所述触发电路的

输出端分别与所述反偏截止驱动单元的输入端和所述晶体管单元的控制端电连接;所述触

发电路用于在所述基于所述电容单元的电压信号输出所述第一驱动信号或所述第二驱动

驱动电路,所述驱动电路的输入端与所述触发电路的输出端电连接,所述驱动电路的

输出端与所述晶体管单元的控制端电连接,所述驱动电路在所述第一驱动信号的作用下驱

动所述晶体管单元关闭,在所述第二驱动信号的作用下驱动所述晶体管单元导通。

4.根据权利要求3所述的理想二极管电路,其特征是,所述触发电路,包括:

电压比较器件,所述电压比较器件的输入端与所述电容单元的第一端电连接,所述电

压比较器件用于在所述电容单元的电压信号小于预设基准电压时输出计时触发信号;

计时触发器件,所述计时触发器件的输入端与所述电压比较器件电连接,所述计时触

发器件的输出端与所述驱动电路的输入端电连接;所述计时触发器件用于在所述计时触发

信号的作用下开始计时,并输出所述第一驱动信号,以及在预设周期时长后输出所述第二

5.根据权利要求4所述的理想二极管电路,其特征是,所述计时触发器件为恒定关断

6.根据权利要求1所述的理想二极管电路,其特征是,所述电压变换单元包括:

低压时钟,分别与所述电荷泵和所述电容单元电连接,所述低压时钟用于在所述电容

7.根据权利要求1所述的理想二极管电路,其特征是,所述晶体管单元包括:金属氧

高压隔离电路,电连接于所述电容单元、所述晶体管单元与所述电压变换单元之间,用

于在所述晶体管单元两端的电压大于预设安全电压时关断所述晶体管单元与所述电容单

9.根据权利要求8所述的理想二极管电路,其特征是,所述高压隔离电路,包括:

电压检测器件,与所述晶体管单元电连接,用于检测所述晶体管单元两端的电压;

第二关断器件,电连接于所述晶体管单元与所述电容单元和/或所述电压变换单元之

间,用于在所述晶体管单元两端的电压大于所述预设安全电压时关断所述晶体管单元与所

10.根据权利要求1所述的理想二极管电路,其特征是,所述晶体管单元采用N沟道

[0001]本发明涉及半导体技术领域,具体地说,涉及一种理想二极管电路。

[0002]理想二极管是指正向压降为0,反向漏电流为0的二极管,传统实现理想二极管的

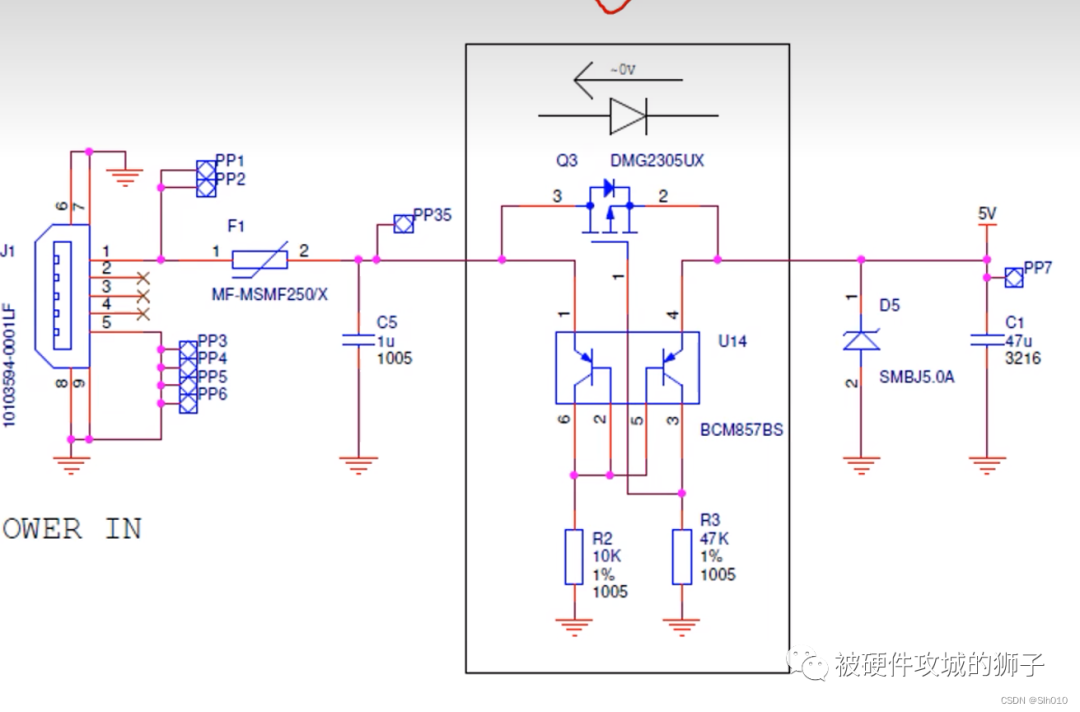

实现方案如图1,电容电压上下限的判断都是利用基准+迟滞比较器完成,为纯模拟的控制

方式,迟滞比较器设计也较为复杂;且在高温小电流下,MOSFET正向体二极管电压VF较小,

电荷泵泵升能力弱,有极大几率会出现一直泵升不到上限电压VCAPH、迟滞比较器时钟达不到翻转

条件,因此导致该理想二级管电路没办法打开MOSFET,无法正常周期性工作。

[0003]例如设置VCAPL=5V,VCAPH=6V,高温小电流下电容电压VF较小,电荷泵电路泵升

能力弱,使得输出电压上限智能达到5.8V,达不到比较器目标上限电压6V,此时迟滞比较器

[0008]电压变换单元,所述电压变换单元分别与所述电容单元与所述晶体管单元电连

接,所述电压变换单元用于通过所述晶体管单元中的寄生二极管对所述电容单元充电;

[0009]控制单元,所述控制单元的输入端与所述电容单元电连接,所述控制单元的输出

端与所述晶体管单元的控制端电连接,所述控制单元用于基于所述电容单元的电压信号输

出第一驱动信号或第二驱动信号,并在所述第一驱动信号的作用下驱动所述晶体管单元关

[0010]反偏截止驱动单元,所述反偏截止驱动单元的输入端与所述电容单元的第一端电

连接,所述反偏截止驱动单元的输出端与所述晶体管单元的控制端电连接,所述反偏截止

驱动单元在所述第一驱动信号的作用下或所述晶体管单元两端的电压反向时驱动所述晶

[0012]反偏检测电路,所述反偏检测电路的第一输入端与所述晶体管单元的控制端电连

接,所述反偏检测电路的第二输入端与所述晶体管单元的电压量测端电连接,所述反偏检

[0013]第一关断器件,所述第一关断器件的输入端与所述反偏检测电路的输出端电连

接,所述反偏检测电路的输出端与所述晶体管单元的控制端电连接,所述第一关断器件用

[0015]触发电路,所述触发电路的控制端与所述电容单元的第一端电连接,所述触发电

路的输出端分别与所述反偏截止驱动单元的输入端和所述晶体管单元的控制端电连接;所

述触发电路用于在所述基于所述电容单元的电压信号输出所述第一驱动信号或所述第二

[0016]驱动电路,所述驱动电路的输入端与所述触发电路的输出端电连接,所述驱动电

路的输出端与所述晶体管单元的控制端电连接,所述驱动电路在所述第一驱动信号的作用

下驱动所述晶体管单元关闭,在所述第二驱动信号的作用下驱动所述晶体管单元导通

[0018]电压比较器件,所述电压比较器件的输入端与所述电容单元的第一端电连接,所

述电压比较器件用于在所述电容单元的电压信号小于预设基准电压时输出计时触发信号;

[0019]计时触发器件,所述计时触发器件的输入端与所述电压比较器件电连接,所述计

时触发器件的输出端与所述驱动电路的输入端电连接;所述计时触发器件用于在所述计时

触发信号的作用下开始计时,并输出所述第一驱动信号,以及在预设周期时长后输出所述

[0020]在本申请一个可选实施例中,所述计时触发器件为恒定关断时间产生器。

[0023]低压时钟,分别与所述电荷泵和所述电容单元电连接,所述低压时钟用于在所述

[0024]在本申请一个可选实施例中,所述晶体管单元包括:金属氧化物半导体场效应晶

[0026]高压隔离电路,电连接于所述电容单元、所述晶体管单元与所述电压变换单元之

间,用于在所述晶体管单元两端的电压大于预设安全电压时关断所述晶体管单元与所述电

[0028]电压检测器件,与所述晶体管单元电连接,用于检测所述晶体管单元两端的电压;

[0029]第二关断器件,电连接于所述晶体管单元与所述电容单元和/或所述电压变换单

元之间,用于在所述晶体管单元两端的电压大于所述预设安全电压时关断所述晶体管单元

[0030]在本申请一个可选实施例中,所述晶体管单元采用N沟道MOS场效应晶体管。

[0031]本申请实施例提供的理想二极管电路中,控制单元的输入端与所述电容单元电连

接,所述控制单元的输出端与所述晶体管单元的控制端电连接,所述控制单元用于基于所

述电容单元的电压信号输出第一驱动信号或第二驱动信号,并在所述第一驱动信号的作用

下驱动所述晶体管单元关闭,在所述第二驱动信号的作用下驱动所述晶体管导通。即使在

高温,小电流情况下,电容单元两端的压降未达到设定的上限电压,控制单元也可以按照预

设周期,的控制晶体管单元的导通与关闭,触发晶体管单元MOSFET关闭后对电容单元进行

泵升。当对电容单元做固定周期的充电后,即再次进行开启,无需等到精确的设定的电压

[0032]同时,在所述晶体管单元两端的电压反向时基于该第一关断器件关闭所述晶体管

[0033]为了更清楚地说明本申请实施例或示例性中的技术方案,下面将对实施例或示例

性描述中所需要用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请

的一些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出

[0038]10、理想二极管电路;110、电容单元;120、晶体管单元;130、电压变换单元;140、控

[0039]为使本申请实施例的目的、技术方案和优点更加清楚,下面将结合本申请实施例

中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是

本申请一部分实施例,而不是全部的实施例,通常在此处附图中描述和示出的本申请实施

[0040]因此,以下对在附图中提供的本申请的实施例的详细描述并非旨在限制要求保护

的本申请的范围,而是仅仅表示本申请的选定实施例,基于本申请中的实施例,本领域普通

技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范

[0041]理想二极管是指正向压降为0,反向漏电流为0的二极管,传统实现理想二极管的

实现方案如图1,电容电压上下限的判断都是利用基准+迟滞比较器完成,为纯模拟的控制

方式,迟滞比较器设计也较为复杂;且在高温小电流下,MOSFET正向体二极管电压VF较小,

电荷泵泵升能力弱,有极大几率会出现一直泵升不到上限电压VCAPH、迟滞比较器时钟达不到翻转

条件,因此导致该理想二级管电路没办法打开MOSFET,无法正常周期性工作。

[0042]例如设置VCAPL=5V,VCAPH=6V,高温小电流下电容电压VF较小,电荷泵电路泵升

能力弱,使得输出电压上限智能达到5.8V,达不到比较器目标上限电压6V,此时迟滞比较器

[0044]基于上述技术问题,请参见图2,本申请实施例提供了一种理想二极管电路10,包

括:电容单元110、晶体管单元120、电压变换单元130和反偏截止驱动单元150,其中:

[0045]相互并联的电容单元110与晶体管单元120;该电容单元110是指用于存储电荷的

器件单元,例如可以包括一个电容单元110,或者多个相互串联的电容单元110。该晶体管单

元120包含一个或多个晶体管,该晶体管是指由三层杂质半导体构成的,具有三个电极的器

件,又称半导体三极管、晶体三极管等,该晶体管可以为普通三极管、场效应管、晶闸管等均

[0046]该电压变换单元130分别与所述电容单元110与所述晶体管单元120电连接,所述

电压变换单元130用于通过所述晶体管单元120中的寄生二极管对所述电容单元110充电。

该电压变换单元130可以为变压器,例如电容电压变换器等,通过该电容电压变换器为电容

单元110进行充电,使得电容单元110的两个极板之间的电压大于该预设基准电压。

[0047]控制单元140,所述控制单元140的输入端与所述电容单元110电连接,所述控制单

元140的输出端与所述晶体管单元120的控制端电连接,所述控制单元140用于基于所述电

容单元110的电压信号周期性输出或者根据电容单元110实际充放电过程输出第一驱动信

号或第二驱动信号,并在所述第一驱动信号的作用下驱动所述晶体管单元120关闭,在所述

第二驱动信号的作用下驱动所述晶体管导通;该控制单元140可以为一集成芯片,也可以由

不同逻辑单元共同构成的控制电路,本申请实施例不作具体限定,可根据真实的情况灵活调

整。例如该晶体管单元120中的晶体管为N型晶体管,该第一驱动信号可以为低电平信号,对

应该第二驱动信号可以为高电平信号,以使得晶体管单元120可以在低电平信号的作用下

关闭,在高电平信号的作用下导通。当然在此仅为对第一驱动信号和第二驱动信号类型的

示例,能够准确的通过晶体管单元120中个晶体管类型进行灵活调整,在此不作具体限定。

[0048]该反偏截止驱动单元150的输入端与所述电容单元110的第一端电连接,所述反偏

截止驱动单元150的输出端与所述晶体管单元120的控制端电连接,所述反偏截止驱动单元

150在所述晶体管单元120两端的电压反向时驱动所述晶体管单元120关闭。

[0049]例如图3中,一般的情况下,晶体管单元120的电流流向为由上及下,即Anode端的电

位高于Cathode的电位,但是一旦电压反向时,Anode端的电位低于Cathode的电位,即可判

断晶体管单元120两端的电压反向,在这种情况下即可关闭晶体管单元120,以实现对晶体

[0051]请继续参见图3与图4,控制单元140基于所述电容单元110的电压信号周期性输出

低电平信号或高电平信号,并在所述低电平信号的作用下驱动所述晶体管单元120关闭,在

所述高电平信号的作用下驱动所述晶体管导通。例如当电容单元110两端的电压信号小于

预设基准电压时,控制单元140输出一低电平信号,所述第一驱动信号的作用下驱动所述晶

体管单元120关闭,在所述第二驱动信号的作用下驱动所述晶体管导通,将晶体管单元120

(MOSFET)两端的压降由VF降低到I*Ron约几十mV,实现理想二极管功能。

[0052]随着晶体管单元120两端的压降降低,电容单元110CAP两端的电压消耗至预设基

准电压(即下限值VCAPL)后,控制单元140再次输出一第一驱动信号(例如低电平信号),在

该低电平信号的作用下驱动该晶体管单元120(MOSFET)关闭,电压变换单元130开始工作,

重新进入为电容单元110充电的周期中。经过固定Toff时间的计时后,再次打开晶体管单元

[0053]本申请实施例提供的理想二极管电路10中,控制单元140的输入端与所述电容单

元110电连接,所述控制单元140的输出端与所述晶体管单元120的控制端电连接,所述控制

单元140用于基于所述电容单元110的电压信号输出第一驱动信号或第二驱动信号,并在所

述第一驱动信号的作用下驱动所述晶体管单元120关闭,在所述第二驱动信号的作用下驱

动所述晶体管导通。即使在高温,小电流情况下,电容单元110两端的压降未达到设定的上

限电压,控制单元140也可根据预设周期,周期性的控制晶体管单元120的导通与关闭,触

发晶体管单元120MOSFET关闭后对电容单元110进行泵升。当对电容单元110进行固定周期

的充电后,即再次进行开启,无需等到精确的设定的电压上限值,实现在极端条件下的工作

[0054]同时,在所述晶体管单元120两端的电压反向时基于该第一关断器件关闭所述晶

[0055]请继续参见图3,在本申请一个可选实施例中,所述反偏截止驱动单元150包括:

[0056]反偏检测电路,所述反偏检测电路的第一输入端与所述晶体管单元120的控制端

电连接,所述反偏检测电路的第二输入端与所述晶体管单元120的电压量测端电连接,所述

[0057]第一关断器件,所述第一关断器件的输入端与所述反偏检测电路的输出端电连

接,所述反偏检测电路的输出端与所述晶体管单元120的控制端电连接,所述第一关断器件

用于在所述晶体管单元120两端的电压反向时驱动所述晶体管单元120关闭。

[0058]本申请实施例基于反偏检测电路检测晶体管单元120的电压方向,然后在所述晶

体管单元120两端的电压反向时基于该第一关断器件关闭所述晶体管单元120,以实现对晶

[0059]请继续参见图3,在本申请一个可选实施例中,所述控制单元140包括:触发电路和

[0060]该触发电路的控制端与所述电容单元110的第一端电连接,所述触发电路的输出

端分别与所述反偏截止驱动单元150的输入端和所述晶体管单元120的控制端电连接;所述

触发电路用于在所述基于所述电容单元110的电压信号周期性输出所述第一驱动信号(例

[0061]该触发电路用于触发驱动电路开始工作,该触发电路的触发信号为电容单元110

两端电压信号的压降大小,例如该压降大于或等于预设基准电压,则输出高电平信号,若该

压降小于预设基准电压,则输出低电平信号。当然在此仅为示例,不构成对本申请实施例控

[0062]该驱动电路的输入端与所述触发电路的输出端电连接,所述驱动电路的输出端与

所述晶体管单元120的控制端电连接,所述驱动电路在所述第一驱动信号(例如低电平信

号)的作用下驱动所述晶体管单元120关闭,在所述第二驱动信号(例如高电平信号)的作用

下驱动所述晶体管单元120导通。该驱动电路能为集成芯片,也可以为设定的电子电路,

本申请实施例不作具体限定,可根据真实的情况灵活调整,只需要能轻松实现基于高电平信号

驱动所述晶体管单元120关闭,在所述高电平信号的作用下驱动所述晶体管单元120导通的

[0063]本申请实施例触发电路基于所述电容单元110的所述电压信号周期性输出所述低

电平信号或所述高电平信号,驱动电路在所述低电平信号的作用下驱动所述晶体管单元

120关闭,在所述高电平信号的作用下驱动所述晶体管单元120导通,将电平信号的产生与

[0064]请继续参见图3,在本申请一个可选实施例中,所述触发电路,包括电压比较器件

[0065]该电压比较器件的输入端与所述电容单元110的第一端电连接,所述电压比较器

件用于在所述电容单元110的电压信号小于预设基准电压时输出计时触发信号;该电压比

较器件用于将电容单元110两端的电压与预设的基准电压作比较,该预设基准电压可以

根据真实的情况设置,例如可以为电容单元110的下限电压VCAPL等,在此不作具体限定,可根

据实际情况灵活调整。该电压比较器件使用普通比较器即可,无需传统中的迟滞比较器,普

[0066]该计时触发器件的输入端与所述电压比较器件电连接,所述计时触发器件的输出

端与所述驱动电路的输入端电连接;所述计时触发器件用于在所述计时触发信号的作用下

开始计时,并输出所述低电平信号,以及在预设周期时长后输出所述高电平信号。

[0067]该计时触发器件至少包含两个功能模块:计时功能模块和电平信号产生模块。该

计时功能模块用于确定信号产生周期,即从开始计时的时刻至预设周期时长通过电平产生

模块生成低电平信号,并在预设周期时长Toff通过电平信号产生模块生成高电平信号。

[0068]在本申请一个可选实施例中,所述计时触发器件为恒定关断时间产生器,又称恒

定关断时间控制器。该恒定关断时间产生器即为在固定时间内进行关断的电子器件,该固

定时间即为上述设定的预设周期时长,在该周期时长内输出低电平信号,在该周期时长后

输出高电平信号,直至在下次接收到计时触发信号(即电容单元110两端的电压信号小于预

设基准电压时输出的触发信号)后又开始计时。该恒定关断时间产生器结构相对比较简单,成本较

低,且可靠性更高,基于该恒定关断时间产生器与其他单元器件来实现本申请实施例的理

[0069]请继续参见图3,在本申请一个可选实施例中,所述电压变换单元130包括:电荷泵

[0070]该电荷泵分别与所述电容单元110和所述晶体管单元120电连接;

[0071]该低压时钟分别与所述电荷泵和所述电容单元110电连接,所述低压时钟用于在

所述电容单元110的电压信号小于预设基准电压时驱动所述电荷泵工作。该低压时钟产生

脉冲信号或者数字信号,通过该脉冲信号或数字信号驱动电荷泵工作。该低压时钟的触发

[0072]本申请实施例通过电荷泵和低压时钟来实现对电容单元110的充电,电荷泵的泵

升能力较强,在较短的时间内将电容单元110的电量充满,提高本申请实施例提供的理想二

[0073]在本申请一个可选实施例中,所述晶体管单元120包括:金属氧化物半导体场效应

物半导体场效应晶体管是一种电压控制元件,以金属层(m)的栅极隔着氧化层(o)利用电场

的效应来控制半导体(s)的场效应晶体管。MOSFET具有输入阻抗高、噪声低、耐热性好、抗

辐射能力强等优点,以及兼有体积小、重量轻等优点,本申请实施例基于该金属氧化物半导

体场效应晶体管与其他单元器件来实现本申请实施例的理想二极管,可靠性更高,且成本

[0074]请继续参见图3,在本申请一个可选实施例中,上述理想二极管电路10,还包括:高

[0075]高压隔离电路,电连接于所述电容单元110、所述晶体管单元120与所述电压变换

单元130之间,用于在所述晶体管单元120两端的电压大于预设安全电压时关断所述晶体管

单元120与所述电容单元110和/或所述电压变换单元130之间的电连接。

[0076]在本申请一个可选实施例中,所述高压隔离电路,包括:电压检测器件和第二关断

[0077]该电压检测器件与所述晶体管单元120电连接,用于检测所述晶体管单元120两端

[0078]该第二关断器件电连接于所述晶体管单元120与所述电容单元110和/或所述电压

变换单元130之间,用于在所述晶体管单元120两端的电压大于所述预设安全电压时关断所

述晶体管单元120与所述电容单元110和/或所述电压变换单元130之间的电连接。

[0079]一旦电压检测器件检测到晶体管单元120两端的电压超出预设安全电压,可以通

过该第二关断器件立刻关断晶体管单元120与所述电容单元110和/或所述电压变换单元

130之间的电连接,以实现对电容单元110和电压变换单元130的保护,提高理想二极管的安

[0080]在本申请一个可选实施例中,所述电容单元110包含一个或多个电容器,通过多个

电容器的并联或者提高单个电容器的容量,提高储能能力,进而提高理想二极管的工作性

[0081]在本申请一个可选实施例中,所述晶体管单元120采用N沟道MOS场效应晶体管,可

以支持高压驱动,即支持本申请实施例电容单元110输出的高电平信号的控制,进而提高本

[0082]以下结合上述所有实施例对本申请实施例提供的理想二极管的工作原理作简要

[0083]请继续参见图2‑图4,电压比较器件对电容单元110CAP两端的电压与预设的基准

电压作比较,当电容单元110两端的电压信号小于预设基准电压时,电压比较器输出一计

时触发信号,该计时触发信号可以为一低电平信号;恒定关断时间产生器在接收到该计时

触发信号后立即启动,开始计时,并输出一低电平信号,驱动电路在该低电平信号的作用下

驱动该晶体管单元120(MOSFET)关闭;恒定关断时间产生器从开始计时开始,在预设周期时

长Toff后输出所述高电平信号,在所述高电平信号的作用下驱动所述晶体管单元120导通,

将晶体管单元120(MOSFET)两端的压降由VF降低到I*Ron约几十mV,实现理想二极管功能。

[0084]随着晶体管单元120两端的压降降低,电容单元110CAP两端的电压消耗至预设基

准电压(即下限值VCAPL)后,电压比较器件再次检测到当电容单元110两端的电压信号小于

预设基准电压时,并输出一计时触发信号,恒定关断时间产生器在接收到该计时触发信号

后立即启动,开始计时,并输出一低电平信号,驱动电路在该低电平信号的作用下驱动该晶

体管单元120(MOSFET)关闭,低电压时钟驱动电荷泵开始工作,重新进入为电容单元110充

电的周期中。经过固定Toff时间的计时后,再次打开晶体管单元120(MOSFET),循环往复,周

[0085]需要解释的是,当电容电压110小于预设下限(VCAPL)后触发恒定关断时间产生器

开始计时,在预设周期时长Toff后输出所述高电平信号,在所述高电平信号的作用下驱动

所述晶体管单元120导通;恒定关断时间产生器在预设周期时长Toff内持续输出一电平信

号,在预设周期时长Toff外输出一高电平信号控制该晶体管单元120(MOSFET)导通,以对储

[0086]以上实施例仅表达了本发明的优选实施方式,其描述较为具体和详细,但并不能

因此而理解为对本发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,

在不脱离本发明构思的前提下,还能做出若干变形、改进及替代,这些都属于本发明的保

2、成为VIP后,下载本文档将扣除1次下载权益。下载后,不支持退款、换文档。如有疑问加。

3、成为VIP后,您将拥有八大权益,权益包括:VIP文档下载权益、阅读免打扰、文档格式转换、高级专利检索、专属身份标志、高级客服、多端互通、版权登记。

4、VIP文档为合作方或网友上传,每下载1次, 网站将按照每个用户上传文档的质量评分、类型等,对文档贡献者给予高额补贴、流量扶持。如果你也想贡献VIP文档。上传文档

抑制灰葡萄孢菌的shRNA与细胞穿膜肽复合物及其制备方法与应用.pdf

氯乙烯单体(Vinyl-Chloride-Monomer)聚氯乙烯(Polyvinyl-Chlor.ppt

鹤煤三矿“无监控不作业”管理制度(试行)(2025.3.13).docx

化工和危险化学品生产经营单位重大生产安全事故隐患自查表实用文档.doc

ISO27001:2022版内部审计划+内审检查表+内审报告全套资料.docx

原创力文档创建于2008年,本站为文档C2C交易模式,即用户上传的文档直接分享给其他用户(可下载、阅读),本站只是中间服务平台,本站所有文档下载所得的收益归上传人所有。原创力文档是网络服务平台方,若您的权利被侵害,请发链接和相关诉求至 电线) ,上传者

上一篇:执行机构论文_我国工控网

Copyright © 2012-2022 竞彩体育比赛现场_竞彩体育彩票直播 版权所有 网站地图